# LH5481 LH5491

# Cascadable $64 \times 8$ FIFO Cascadable $64 \times 9$ FIFO

# FEATURES

- Fastest 64 × 8/9 Cascadable FIFO 35/25/15 MHz

- Expandable in Word Width and FIFO Depth

- Almost-Full/Almost-Empty and Half-Full Flags

- Fully Independent Asynchronous Inputs and Outputs

- LH5481 Output Enable forces Data Outputs to High-Impedance State

- Pin-Compatible Replacements for Cypress CY7C408A/09A or Logic Devices L8C408/09 FIFOs

- Industry Standard Pinout

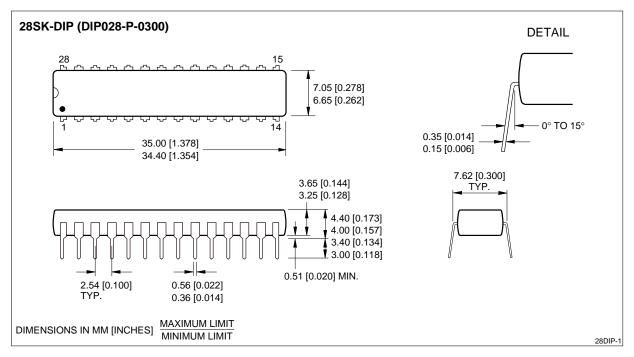

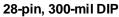

- Packages: 28-Pin, 300-mil DIP 28-Pin PLCC

# FUNCTIONAL DESCRIPTION

The LH5481 and LH5491 are high-performance, asynchronous First-In, First-Out (FIFO) memories organized 64 words deep by eight or nine bits wide. The eight-bit LH5481 has an Output Enable ( $\overline{OE}$ ) function, which can be used to force the eight data outputs (DO) to a high-impedance state. The LH5491 has nine data outputs.

These FIFOs accept eight or nine-bit data at the Data Inputs (DI). A Shift In (SI) signal writes the DI data into the FIFO. A Shift Out (SO) signal shifts stored data to the Data Outputs (DO). The Output Ready (OR) signal indicates when valid data is present on the DO outputs.

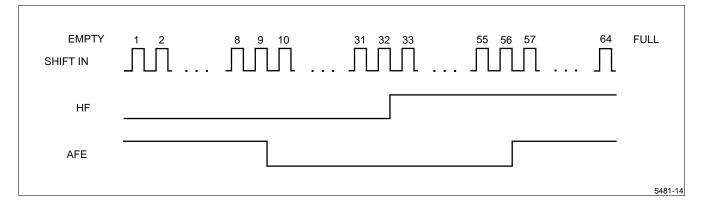

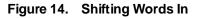

If the FIFO is full and unable to accept more DI data, Input Ready (IR) will not return HIGH, and SI pulses will be ignored. If the FIFO is empty and unable to shift data to the DO outputs, OR will not return HIGH, and SO pulses will be ignored. The Almost-Full/Almost-Empty (AFE) flag is asserted (HIGH) when the FIFO is almost-full (56 words or more) or almost- empty (eight words or less). The Half-Full (HF) flag is asserted (HIGH) when the FIFO contains 32 words or more.

Reading and writing operations may be asynchronous, allowing these FIFOs to be used as buffers between digital machines of different operating frequencies. The high speed makes these FIFOs ideal for high performance communication and controller applications.

# **PIN CONNECTIONS**

| 28-PIN PDIP        |    |                      | TOP VIEW |

|--------------------|----|----------------------|----------|

| AFE [              | 1• | 28 🗆 V <sub>CC</sub> |          |

| HF                 | 2  | 27 🗌 MR              |          |

| IR [               | 3  | 26 🗆 SO              |          |

| SI [               | 4  | 25 🗌 OR              |          |

|                    | 5  | 24 🗖 DO₀             |          |

| DI <sub>1</sub>    | 6  | 23 🗌 DO1             |          |

| V <sub>SS</sub> [  | 7  | 22 🗆 V <sub>SS</sub> |          |

| DI <sub>2</sub>    | 8  | 21 🗌 DO <sub>2</sub> |          |

| DI <sub>3</sub>    | 9  | 20 🗆 DO <sub>3</sub> |          |

| DI <sub>4</sub>    | 10 | 19 🗌 DO4             |          |

| DI <sub>5</sub>    | 11 | 18 ☐ DO₅             |          |

| DI <sub>6</sub>    | 12 | 17 🗌 DO <sub>6</sub> |          |

| DI <sub>7</sub>    | 13 | 16 🗆 DO <sub>7</sub> |          |

| NC/DI <sub>8</sub> | 14 |                      |          |

|                    | L  |                      | 5481-1D  |

Figure 1. Pin Connections for DIP Package

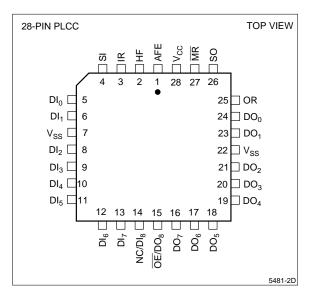

Figure 2. Pin Connections for PLCC Package

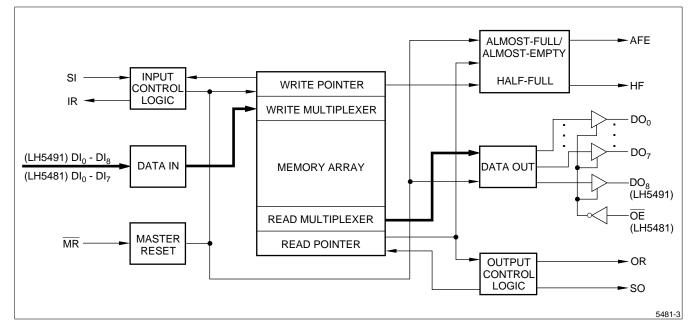

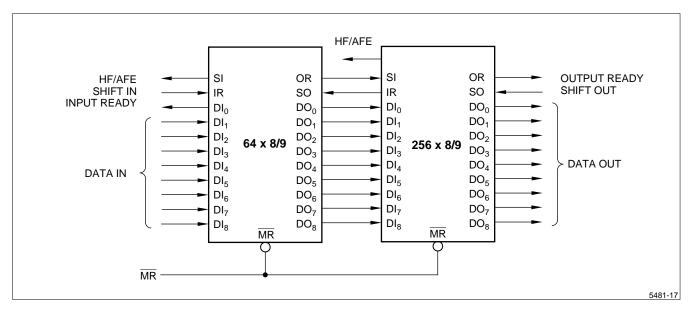

Figure 3. LH5481/91 Block Diagram

#### **PIN DESCRIPTIONS**

| PIN           | PIN TYPE * | DESCRIPTION          |

|---------------|------------|----------------------|

| $DI_0 - DI_7$ | I          | Data Inputs, LH5481  |

| $DO_0 - DO_7$ | O/Z        | Data Outputs, LH5481 |

| $DI_0 - DI_8$ | I          | Data Inputs, LH5491  |

| $DO_0 - DO_8$ | 0          | Data Outputs, LH5491 |

| SI            | I          | Shift In             |

| SO            | I          | Shift Out            |

| IR            | 0          | Input Ready          |

| OR            | 0          | Output Ready         |

\* I = Input, O = Output, Z = High-Impedance, V = Power Voltage Level

| PIN             | PIN TYPE * | DESCRIPTION                    |

|-----------------|------------|--------------------------------|

| HF              | 0          | Half-Full Flag                 |

| AFE             | 0          | Almost-Full / Almost-<br>Empty |

| MR              | I          | Master Reset                   |

| ŌĒ              | I          | Output Enable<br>(LH5481 only) |

| V <sub>CC</sub> | V          | Positive Power Supply          |

| V <sub>SS</sub> | V          | Ground                         |

# ABSOLUTE MAXIMUM RATINGS 1,2

| PARAMETER                                     | RATING                                    |

|-----------------------------------------------|-------------------------------------------|

| Vcc Range                                     | -0.5 V to 7 V                             |

| Input Voltage Range                           | -0.5 V to Vcc + 0.5 V (not to exceed 7 V) |

| DC Output Current <sup>3</sup>                | ±40 mA                                    |

| Storage Temperature                           | -65°C to 150°C                            |

| DC Voltage Applied To Outputs In High-Z state | -0.5 V to Vcc + 0.5 V (not to exceed 7 V) |

| Static Discharge Voltage <sup>4</sup>         | > 2000 V                                  |

| Power Dissipation (Package Limit)             | 1.0 W                                     |

NOTES:

1. All voltages are measured with respect to Vss.

2. Stresses greater than those listed under 'Absolute Maximum Ratings' may cause permanent damage to the device. This is a stress rating for transient conditions only. Functional operation of the device at these or any other conditions above those indicated in the 'Operating Range' of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

3. Outputs should not be shorted for more than 30 seconds. No more than one output should be shorted at any time.

4. Sample tested only.

# **OPERATING RANGE**<sup>1</sup>

| PARAMETER       | DESCRIPTION                                | MIN  | MAX       | UNIT |

|-----------------|--------------------------------------------|------|-----------|------|

| T <sub>A</sub>  | Temperature, Ambient                       | 0.0  | 70        | °C   |

| V <sub>CC</sub> | Supply Voltage                             | 4.5  | 5.5       | V    |

| Vss             | Ground                                     | 0.0  | 0.0       | V    |

| VIL             | Input Low Voltage (Logic '0') <sup>2</sup> | -0.5 | 0.8       | V    |

| V <sub>IH</sub> | Input High Voltage (Logic '1')             |      | Vcc + 0.5 | V    |

NOTES:

1. All voltages are measured with respect to Vss.

2. FIFO inputs are able to withstand a -1.5 V undershoot for less than 10 ns per cycle.

# **DC ELECTRICAL CHARACTERISTICS**<sup>1</sup> (Over Operating Range Unless Otherwise Noted)

| PARAMETER       | DESCRIPTION                       | TEST CONDITIONS                                                                                                              | MIN | MAX | UNIT |

|-----------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| ILI             | Input Leakage Current             | $V_{CC}$ = 5.5 V, $V_{IN}$ = 0 V to $V_{CC}$                                                                                 | -10 | 10  | μA   |

| ILO             | Output Leakage Current (High-Z)   | $V_{CC}$ = 5.5 V, $V_{OUT}$ = 0 V to $V_{CC}$                                                                                | -10 | 10  | μA   |

| V <sub>OH</sub> | Output High Voltage               | $V_{CC} = 4.5 \text{ V}, I_{OH} = -4 \text{ mA}$                                                                             | 2.4 |     | V    |

| Vol             | Output Low Voltage                | $V_{CC} = 4.5 \text{ V}, I_{OL} = 8.0 \text{ mA}$                                                                            |     | 0.4 | V    |

| Iccq            | Power Supply Quiescent Current    | $\label{eq:VCC} \begin{split} V_{CC} &= 5.5 \ V, \ I_{OUT} = 0 \ mA \\ V_{IN} \leq V_{IL}, \ V_{IN} \geq V_{IH} \end{split}$ |     | 25  | mA   |

| Icc             | Power Supply Current <sup>2</sup> | fsi = 35 MHz, fso = 35 MHz                                                                                                   |     | 45  | mA   |

#### NOTES:

1. All voltages are measured with respect to Vss.

2. Icc is dependent upon actual output loading and cycle rates. Specified values are with outputs open.

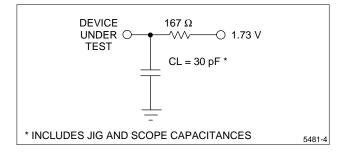

# AC TEST CONDITIONS<sup>1</sup>

| PARAMETER                             | RATING    |  |  |

|---------------------------------------|-----------|--|--|

| Input Pulse Levels                    | 0 to 3 V  |  |  |

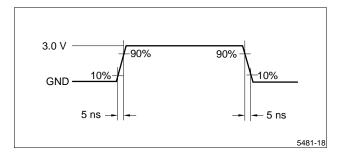

| Input Rise and Fall Times (10% / 90%) | Figure 4a |  |  |

| Input Timing Reference Levels         | 1.5 V     |  |  |

| Output Timing Reference Levels        | 1.5 V     |  |  |

| Output Load for AC Timing Tests       | Figure 4b |  |  |

#### NOTE:

1. All voltages are measured with respect to Vss.

# CAPACITANCE 1,2

| PARAMETER | DESCRIPTION        | TEST CONDITIONS                                   | RATING |

|-----------|--------------------|---------------------------------------------------|--------|

| CIN       | Input Capacitance  | $T_A = 25^{\circ}C$ , f = 1 MHz, $V_{CC} = 4.5 V$ | 5 pF   |

| Соит      | Output Capacitance | $T_A = 25^{\circ}C$ , f = 1 MHz, Vcc = 4.5 V      | 7 pF   |

#### NOTES:

- 1. All voltages are measured with respect to Vss.

- 2. Sample tested only.

Figure 4a. Input Rise and Fall Times

#### Figure 4b. Output Load Circuit

# AC ELECTRICAL CHARACTERISTICS<sup>1</sup> (Over Operating Range)

| SYMBOL             | PARAMETER                                 | 151 | MHz | 251 | MHz | 35M Hz |     | UNITS |

|--------------------|-------------------------------------------|-----|-----|-----|-----|--------|-----|-------|

| STMBOL             |                                           | MIN | MAX | MIN | MAX | MIN    | MAX |       |

| fo                 | Operating Frequency <sup>2</sup>          |     | 15  |     | 25  |        | 35  | MHz   |

| tphsi              | SI HIGH Time <sup>3,8</sup>               | 15  |     | 11  |     | 9      |     | ns    |

| <b>t</b> PLSI      | SI LOW Time <sup>3,8</sup>                | 20  |     | 18  |     | 17     |     | ns    |

| t <sub>SSI</sub>   | Data Setup to SI <sup>4</sup>             | -1  |     | -1  |     | -1     |     | ns    |

| t <sub>HSI</sub>   | Data Hold from SI <sup>4</sup>            | 14  |     | 12  |     | 10     |     | ns    |

| t <sub>DLIR</sub>  | Delay, SI HIGH to IR LOW                  |     | 20  |     | 18  |        | 16  | ns    |

| t <sub>DHIR</sub>  | Delay, SI LOW to IR HIGH                  |     | 24  |     | 20  |        | 18  | ns    |

| <b>t</b> PHSO      | SO HIGH Time <sup>3</sup>                 | 15  |     | 11  |     | 9      |     | ns    |

| tpls0              | SO LOW Time <sup>3</sup>                  | 20  |     | 18  |     | 17     |     | ns    |

| t <sub>DLOR</sub>  | Delay, SO HIGH to OR LOW                  |     | 20  |     | 18  |        | 16  | ns    |

| t <sub>DHOR</sub>  | Delay, SO LOW to OR HIGH                  |     | 24  |     | 20  |        | 18  | ns    |

| tSOR               | Data Setup to OR HIGH                     | -1  |     | -1  |     | -1     |     | ns    |

| t <sub>HSO</sub>   | Data Hold from SO LOW                     | 0   |     | 0   |     | 0      |     | ns    |

| tFT                | Fallthrough Time                          |     | 36  |     | 34  |        | 30  | ns    |

| tвт                | Bubblethrough Time                        |     | 28  |     | 26  |        | 25  | ns    |

| t <sub>SIR</sub>   | Data Setup to IR <sup>5</sup>             | 5   |     | 5   |     | 5      |     | ns    |

| t <sub>HIR</sub>   | Data Hold from IR <sup>5</sup>            | 5   |     | 5   |     | 5      |     | ns    |

| t <sub>PIR</sub>   | Input Ready Pulse HIGH <sup>8</sup>       | 7   |     | 7   |     | 7      |     | ns    |

| t <sub>POR</sub>   | Output Ready Pulse HIGH <sup>8</sup>      | 7   |     | 7   |     | 7      |     | ns    |

| <b>T</b> DLZOE     | OE LOW to LOW Z (LH5481) 6,9              |     | 35  |     | 30  |        | 25  | ns    |

| <b>t</b> DHZOE     | OE HIGH to HIGH Z (LH5481) <sup>6,9</sup> |     | 35  |     | 30  |        | 25  | ns    |

| t <sub>DHHF</sub>  | SI LOW to HF HIGH                         |     | 40  |     | 40  |        | 36  | ns    |

| t <sub>DLHF</sub>  | SO LOW to HF LOW                          |     | 40  |     | 40  |        | 36  | ns    |

| t <sub>DLAFE</sub> | SO or SI LOW to AFE LOW                   |     | 40  |     | 40  |        | 36  | ns    |

| t <sub>DHAFE</sub> | SO or SI LOW to AFE HIGH                  |     | 40  |     | 40  |        | 36  | ns    |

| t <sub>PMR</sub>   | MR Pulse Width                            | 35  |     | 35  |     | 35     |     | ns    |

| tDSI               | MR HIGH to SI HIGH                        |     | 25  |     | 25  |        | 22  | ns    |

| t <sub>DOR</sub>   | MR LOW to OR LOW <sup>7</sup>             |     | 25  |     | 25  |        | 20  | ns    |

| t <sub>DIR</sub>   | MR LOW to IR HIGH <sup>7</sup>            |     | 25  |     | 25  |        | 20  | ns    |

| t <sub>LXMR</sub>  | MR LOW to Output LOW <sup>7</sup>         |     | 25  |     | 25  |        | 20  | ns    |

| tAFE               | MR LOW to AFE HIGH                        |     | 30  |     | 30  |        | 30  | ns    |

| tHF                | MR LOW to HF LOW                          |     | 30  |     | 30  |        | 30  | ns    |

| top                | SO LOW to Next Data Out Valid             |     | 26  |     | 22  |        | 20  | ns    |

NOTES:

1. All time measurements performed at 'AC Test Conditions.'

$2. \quad f_O=f_{SI}=f_{SO}.$

- 3.  $t_{PHSI} + t_{PLSI} = t_{PHSO} + t_{PLSO} = I/f_O.$

- $4~~t_{SSI}$  and  $t_{HSI}$  apply when memory is not full.

- 5. tsir and thir apply when memory is full and SI is HIGH.

- 6. High-Z transitions are referenced to the steady-state  $V_{OH}$  500 mV and  $V_{OL}$  + 500 mV levels on the output.

- 7. After reset goes LOW, all Data outputs will be at LOW level, IR goes HIGH and OR goes LOW.

- 8. Common dash number devices are guaranteed by design to function properly in a cascaded configuration.

9. Sample tested only.

### **OPERATIONAL DESCRIPTION**

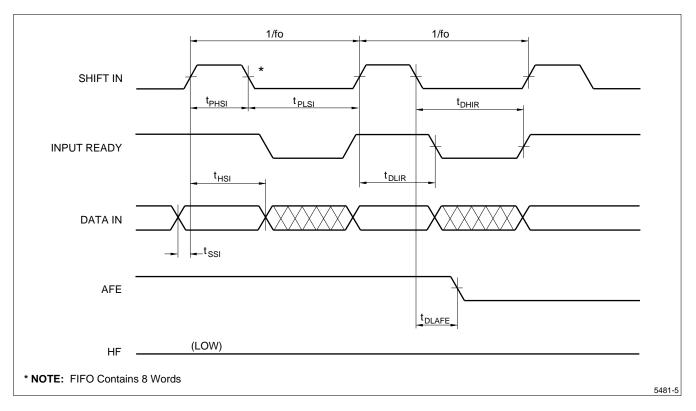

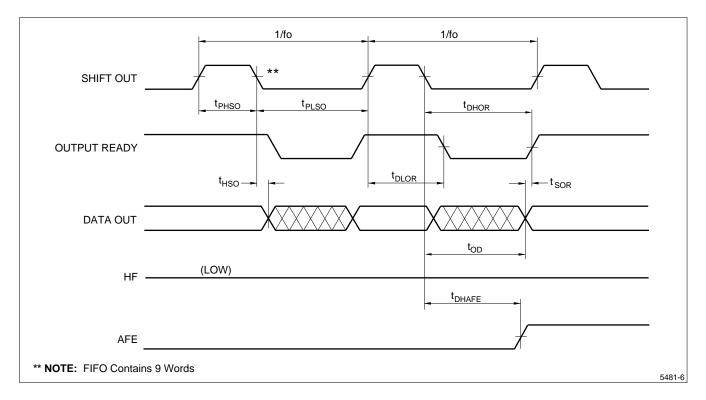

Unlike earlier versions of FIFOs, the LH5481 and LH5491 use dual-port Random-Access-Memory, write and read pointers, and special control logic. The write pointer is incremented by the falling edge of the Shift In (SI) signal, while the read pointer is incremented by the falling edge of the Shift Out (SO) signal. The Input Ready (IR) signal enables data writing to the FIFO. The Output Ready (OR) signal indicates valid read information is available on the Data Output (DO) pins.

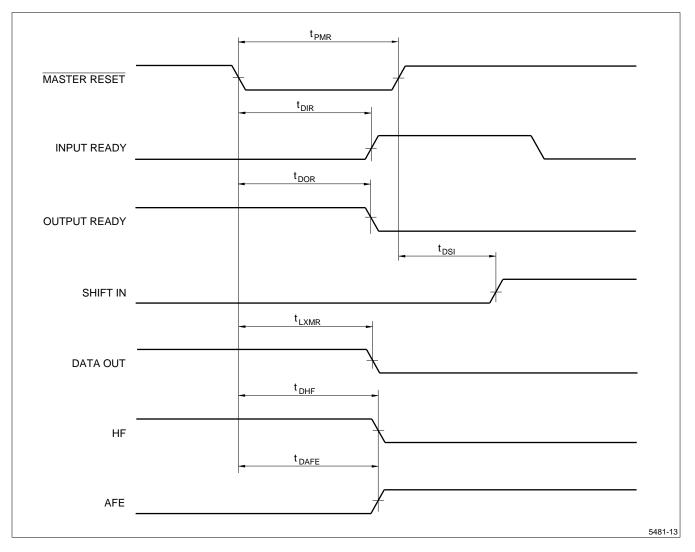

#### **Resetting The FIFO**

The FIFO must be reset, upon power-up, using the Master Reset (MR) signal. This causes the FIFO to enter an empty state, indicated by the Output Ready (OR) being LOW and Input Ready (IR) being HIGH. All Data Output (DO) pins will be LOW in this state. The AFE flag will be HIGH, and the HF flag will be LOW.

If Shift In (SI) is HIGH, when the Master Reset ( $\overline{MR}$ ) signal is ended, then the data on the Data Input (DI) pins will be written into the FIFO, and Input Ready (IR) will return LOW until Shift In (SI) is brought LOW.

If Shift In (SI) is LOW when the Master Reset (MR) is deasserted, then Input Ready (IR) goes HIGH, but the data on the Data Input (DI) pins does not enter the FIFO until Shift In (SI) goes HIGH.

#### Shifting Data In

Data Input (DI) is shifted into the FIFO on the rising edge of Shift In (SI). This loads input data into the FIFO, and causes Input Ready (IR) to go LOW. When a falling edge of Shift In (SI) occurs,the write pointer increments to the next word position, and Input Ready (IR) goes HIGH, indicating that the FIFO is ready to accept new data. When the FIFO is full, Input Ready (IR) remains LOW after the negative edge of Shift In (SI) signal; Shift Out (SO) action is required to unload a word of data and bring Input Ready (IR) HIGH. (See 'Bubblethrough Condition' description.)

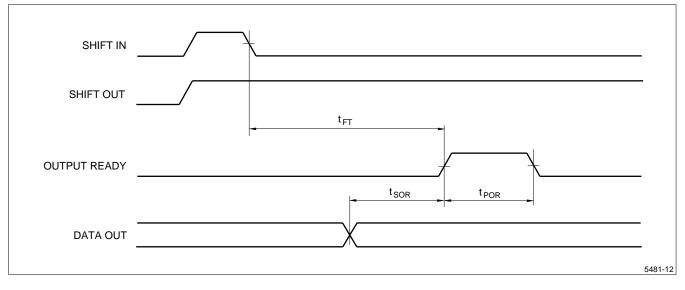

#### **Shifting Data Out**

Data is shifted out of the FIFO on the falling edge of Shift Out (SO). The read pointer increments to the next

word location; FIFO data, if present, appears on the Data Output (DO) pins; and the Output Ready (OR) signal goes HIGH. If FIFO data is not present, Output Ready (OR) stays LOW, indicating that the FIFO is empty; in this case, the last valid data read from the FIFO remains on the Data Output (DO) pins. When the FIFO is not empty, Output Ready (OR) goes LOW after the rising edge of Shift Out (SO). The previous data remains on the Data Output (DO) pins until a falling edge of Shift Out (SO).

#### **Fallthrough Condition**

When the FIFO is empty, a data word entering through the Shift In (SI) action follows one of two sequences.

If Shift Out (SO) is LOW, the data propagates to the Data Output (DO) pins; and Output Ready (OR) goes HIGH and stays HIGH until the next rising edge of Shift Out (SO).

If Shift Out (SO) is held HIGH while data is shifted into an empty FIFO as occurs in depth cascading of FIFOs, data propagates to the Data Output (DO) pins, and Output Ready (OR) pulses HIGH for a minimum time duration specified by tPOR and then goes back LOW again. The stored word remains on the Data Output (DO) pins. If more words are written into the FIFO, they line up behind the first word, and do not appear on the Data Output (DO) pins until Shift Out (SO) has returned LOW.

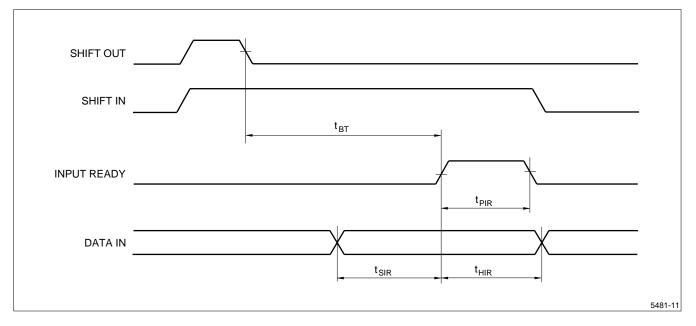

#### **Bubblethrough Condition**

When the FIFO is full, Shift Out (SO) action initiates one of the following two sequences:

If Shift In (SI) is LOW, Input Ready (IR) goes HIGH and stays HIGH until the next rising edge of Shift In (SI).

If Shift In (SI) is held HIGH while data is shifted out of a full FIFO, as occurs in depth cascading of FIFOs, Input Ready (IR) pulses HIGH for a minimum time duration specified by  $t_{PIR}$ , and then goes back LOW again. Special Data Input (DI) setup and hold times ( $t_{SIR}$  and  $t_{HIR}$ , respectively) are defined for this condition.

# TIMING DIAGRAMS

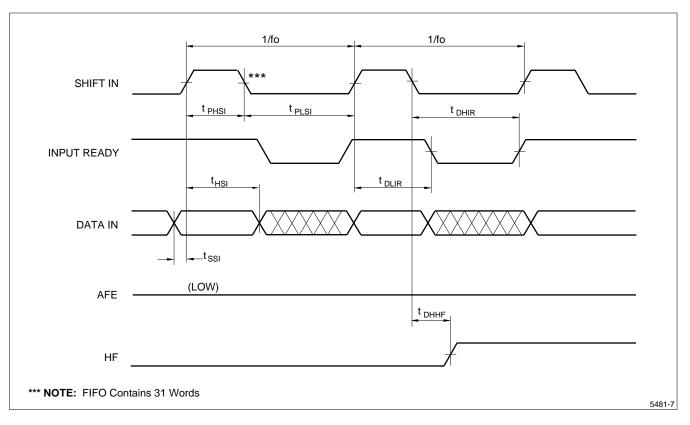

Figure 7. Data In Timing

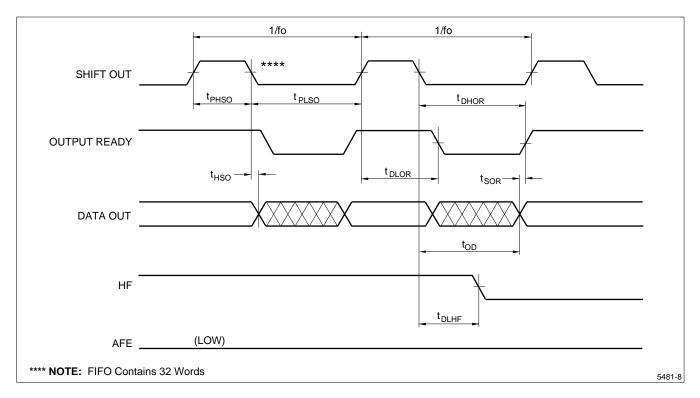

Figure 8. Data Out Timing

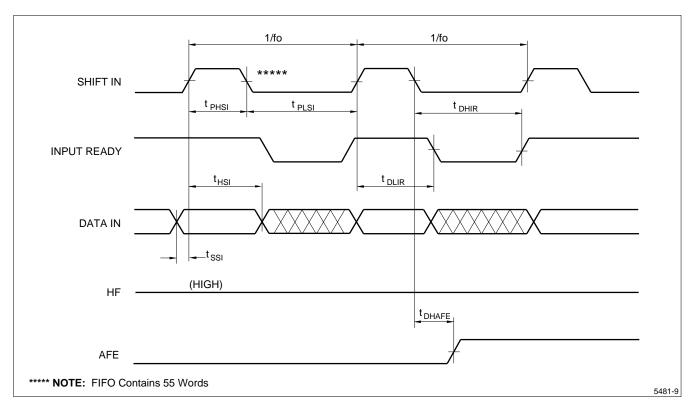

Figure 11. Bubblethrough Timing (Reading a Full FIFO)

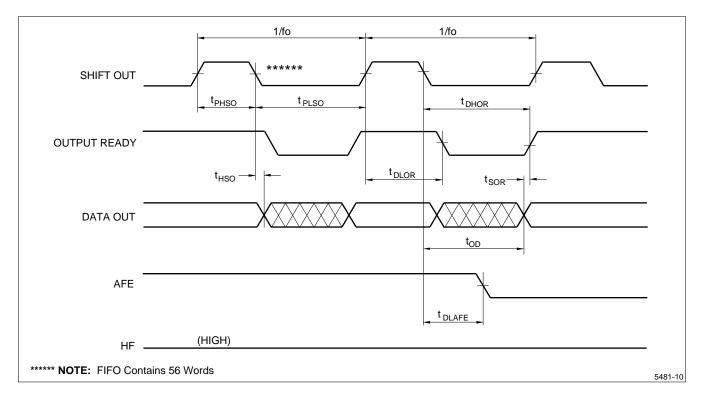

Figure 12. Fallthrough Timing (Writing an Empty FIFO)

Figure 13. Master Reset Timing

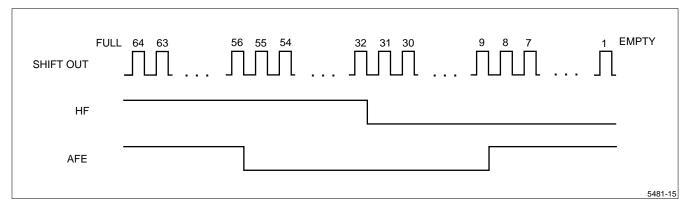

# **FIFO EXPANSION**

Figure 16.  $320 \times 24/27$  Configuration Using  $64 \times 8/9$  (LH5481/91) & 256  $\times 8/9$  (LH5485/95) FIFOs

# FIFO EXPANSION (cont'd)

Figure 17.  $128 \times 8/9$  Configuration

FIFOs are expandable in depth and width. However, in forming wider words, external logic is required to generate composite Input Ready and Output Ready flags. This is due to the variation of delays of the FIFOs. For example, the circuit of Figure 16 uses simple AND gates as the external IR and OR generators. More complex logic may be required if fallthrough and bubblethrough pulses are needed by the external system.

FIFOs can be easily cascaded to any desired depth, as illustrated in Figure 17. The handshaking and associated timing between the FIFOs are handled by the inherent timing of the devices.

#### NOTES:

- When the memory is empty, the last word read remains on the outputs until Master Reset is strobed, or a new data word bubbles through to the output. However, OR remains LOW, indicating that the data word at the output is not valid.

- 2. When the output data word changes as a result of a pulse on SO, the OR signal always goes LOW before the output data word changes and stays LOW until a new data word has appeared at the outputs. Anytime OR is HIGH, there is valid stable data on the outputs.

- 3. All SHARP FIFOs can be cascaded with other SHARP FIFOs of the same architecture (i.e.,  $64 \times 8/9$  with  $64 \times 8/9$ ). However, they may not cascade with FIFOs from other manufacturers.

# PACKAGE DIAGRAMS

28-pin, 450-mil PLCC

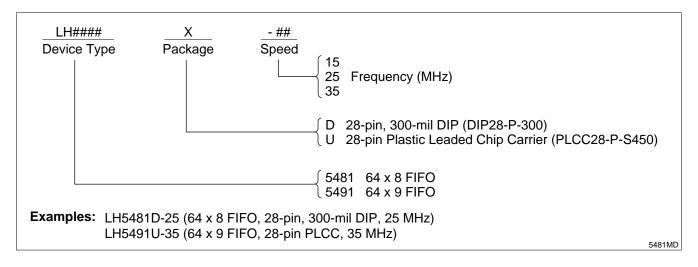

## **ORDERING INFORMATION**